업계 최초 20나노 올 프로그래머블 디바이스 개발 완료

자일링스는 28나노에서 시작된 산업 혁신을 확장하며, 2개의 최초 20나노 기술을 발표했다.

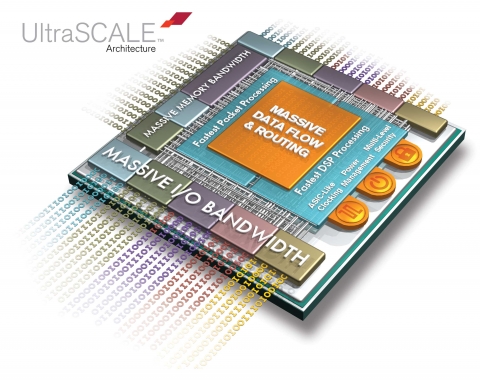

자일링스는 반도체 업계 최초 20나노 디바이스와 PLD 업계 최초로 20나노 올 프로그래머블 디바이스 개발을 완료했다. 또한, 업계 최초의 ASIC 클래스 프로그래머블 아키텍처인 울트라스케일(UltraScale)™도 함께 선보였다. 업계 최초 28 나노 개발 완료, 올 프로그래머블 SoC, 올 프로그래머블 3D IC, SoC 강도 디자인 수트 발표 등 자일링스는 연이어 앞선 기술을 시장에 출시하고 있다.

자일링스의 플랫폼 개발 수석 부사장인 빅터 펭(Victor Peng)은 “업계에서 훨씬 앞선 20나노 개발 완료를 통해 알 수 있듯이, 자일링스의 기술력은 경쟁사들보다 고급 디바이스는 1 년 이상, 중급 디바이스에서는 반 년 이상 더 앞서 있다.”라고 말하며, “TSMC의 기술과 자사의 울트라스케일 아키텍처, 비바도® 디자인 수트와의 최적화를 통해, 자일링스는 경쟁사보다 1년 이상 앞선 기술력으로 1.5~2배 이상의 신뢰성 있는 시스템 레벨 성능과 통합을 제공한다. 이는 자일링스가 경쟁사보다 한 세대 앞선 기업임을 증명하는 것이다.”라고 덧붙였다.

자일링스는 28HPL의 개발 과정에서 그랬듯이, TSMC와 협력하여 고급 FPGA 요건을 TSMC 20SoC 개발 공정에 적용했다. 이러한 28나노 협력은 업계 최초의 28나노 개발 완료, 업계 최초의 올 프로그래머블 FPGA, SoC, 3D IC 디바이스로 이어졌으며, 이로 인해 자일링스는 가격, 성능, 와트, 프로그래머블 시스템 통합, BOM 비용 절감 등 다방면에서 한 세대 앞선 위치에 자리매김 하였다. 자일링스는 업계 최초로 ASIC 클래스 프로그래머블 아키텍처인 울트라스케일의 개발을 완료하며, 28나노에 이어 20나노 산업에서도 다시 한번 업계 리더임을 입증했다.

울트라스케일 아키텍처는 20나노 평면부터 16나노를 거쳐 핀펫(FinFET) 기술 너머까지, 모놀리식부터 3D IC까지 이르는 단계까지 확장되도록 개발되었다. 이 아키텍처는 총 시스템 스루풋(throughput)과 레이턴시(latency)의 확장에 가해지는 한계들을 처리할 뿐만 아니라, 고급 노드에서의 칩 성능, 인터커넥트에서 가장 큰 문제인 병목현상도 처리하고 있다.

혁신적인 아키텍처 방식은 전체 라인 레이트에서 스마트 공정으로 초당 수 백 기가 비트 레벨의 시스템 성능 관리와 테라비트(terabit)와 테라플롭(teraflop)까지의 확장이 필요하다. 각 트랜지스터나 시스템 블록의 성능을 증가시키거나 시스템 내 블록의 수를 확대시키는 것뿐만 아니라, 통신, 클록킹(clocking), 크리티컬 경로, 인터커넥트를 근본적으로 개선하여 방대한 데이터 흐름 및 실시간 패킷, DSP, 이미지 프로세싱 등을 처리해야 한다. 울트라스케일 아키텍처는 올 프로그래머블 아키텍처에서 최신 ASIC 기법을 적용하여 이러한 문제들을 해결하고 있다:

- 멀티 테라비트 처리량을 지원하는 와이드 버스에 최적화된 방대한 데이터 플로우

- 멀티 영역 ASIC과 유사한 클로킹, 전원 관리, 차세대 보안

- 고도로 최적화된 크리티컬 경로와 내장 고속 메모리, DSP 및 패킷 프로세싱에서 병목현상을 없애는 캐스케이드(cascade)

- 2세대 3D IC 시스템 통합을 위한 인터 다이(inter-die) 대역폭에서의 획기적 성능 향상

- 방대한 I/O 및 메모리 대역폭과 획기적인 레이턴시 감소, 3D IC 와이드 메모리 최적화 인터페이스

- 라우팅(routing) 정체 제거, 비바도 툴을 이용해 90% 이상의 상호 최적화

초기 울트라스케일 디바이스는 이미 시장을 선도하고 있는 28나노 프로세스 기술 기반의 버텍스(Virtex)® 및 킨텍스(Kintex)® FPGA와 3D IC 제품군을 더욱 확장하고 향후 Zynq® 울트라스케일 올 프로그래머블 SoC의 초석이 될 것이다. 이와 같은 확장을 통해 다음과 같은 고성능 아키텍처 요건을 가진 차세대 스마터 시스템이 가능해 진다:

- 400G OTN과 지능형 패킷 프로세싱, 트래픽 관리

- 4X4 복합 모드(Mixed Mode) LTE 및 스마트 빔포밍(beamforming) WCDMA 무선

- 스마트 이미지 강화 및 인식 4K2K 및 8K 디스플레이

- ISR(intelligence surveillance and reconnaissance)을 위한 최고 성능의 시스템

- 데이터 센터를 위한 고성능 컴퓨팅 애플리케이션

자일링스의 CEO 모쉬 가브리엘로브(Moshe Gavrielov)는 “업계 최초의 20나노 개발 완료, 최초의 ASIC 클래스 울트라스케일 아키텍처, 최초의 SoC 강도 비바도 디자인 수트, 지속적으로 확장 중인 IP, C, 스마터 시스템을 위한 ARM® 프로세서 기반 솔루션 등을 통해 자일링스는 다시 한 번 PLD 산업의 가치와 시장을 확장하고 있다. 또한 자일링스는 고객에게 경쟁사보다 1년 앞선 세대를 뛰어넘는 가치를 전달하고 있다.”라고 덧붙였다.

공급 시기

울트라스케일 기반 FPGA를 지원하는 비바도 디자인 수트의 얼리 액세스는 현재 이용 가능하다. 초기 울트라스케일 디바이스는 2013년 4분기로 예정되어 있으며, 자세한 내용은 www.xilinx.com/ultrascale 에서 확인할 수 있다.